# THE 8563 VIDEO CONTROLLER

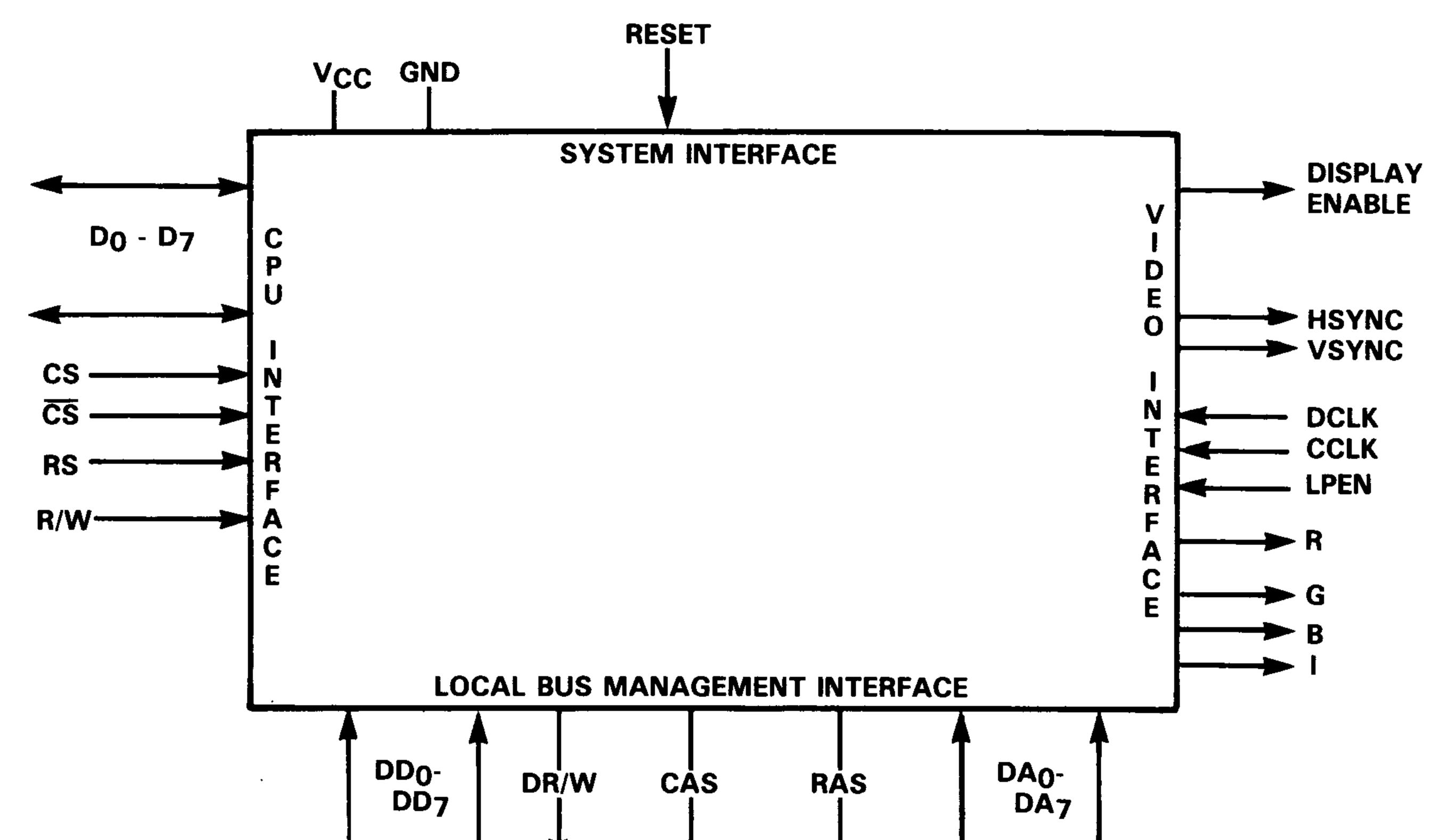

The 8563 is a HMOSII technology, custom, 80 column, color video display controller. The 8563 supplies all necessary signals to directly interface to 16K of DRAM, including refresh, and generates RGBI for use with an external RGBI monitor.

There are many different signals involved with the 8563 chip, but they can generally be divided into three categories. The CPU Interface signals serve as an interface to the 8502 bus. The Local Bus Management signals serve to maintain the local memory bus. Finally, the Video Interface signals are those signals that are necessary to provide an RGBI image on an RGBI monitor.

The 8563 chip interfaces directly to the 8502 bus using a minimum of signals. This is due mainly to the local memory used by the 8563.

The Local Bus Management Interface is a group of signals generated by the 8563 for the management of local video DRAM. This local DRAM both simplifies the addition of an 80 column video display to the system and enables it to support an 80 column display without taxing its memory resources.

The final set of 8563 signals are the Video Interface signals. These signals are directly related to the displayed video image.

## THE 8563 VIDEO CONTROLLER (Continued)

#### **External Registers**

The 8563, which sits at \$D600 in the C128, appears to the user as a device consisting of only two registers. These two registers are indirect registers which must be programmed to access the internal set of thirty-seven programming registers. The first register, located at \$D600, is called the Address/Status register. When written to, the five least significant bits convey the address of an internal register to be accessed in some way. On a read of this register, a status byte is returned. Bit 7 of this register is low while display memory is being updated, and goes high when ready for the next operation. The 6th bit will return low for a light pen register invalid condition and high for a valid light pen address. The final register indicates with a low that the scan is not in vertical blanking, high that it is in vertical blanking.

The other register is the data register. It can be read and written to. Its purpose is to write data to the internal register selected by the Address register. All internal registers can be read and written to through this register, though not all of them are a full eight bits wide.

### **Internal Registers**

I here are thirty-seven internal registers in the 8563, used for a variety of operations. They fall into two basic groups — setup registers and display registers. Setup registers are used to define internal counts for proper video display.

The display registers are used to define and manipulate characters on the screen. Once a character set has been downloaded to the chip, it is possible to display 80 column text in 4-bit digital color. There are also block movement commands that remove the time overhead needed to load large amounts of data to the chip through the two levels of indirection. Below is a display of the 8563 internal register map.

|            | Bit 7   Bit 6   Bit 5   Bit 4   Bit 3   Bit 2   Bit 1   Bit 0 |  |  |  |  |  |  |

|------------|---------------------------------------------------------------|--|--|--|--|--|--|

| 800        | Horizontal Total                                              |  |  |  |  |  |  |

| R01        | Horizontel Displayed                                          |  |  |  |  |  |  |

| R02        | Horizontel Sync Position                                      |  |  |  |  |  |  |

| R03        | Vertical Sync Width Horizontal Sync Width                     |  |  |  |  |  |  |

| ROU        | Vertical Total                                                |  |  |  |  |  |  |

| R05        | Vertical Total Adjust                                         |  |  |  |  |  |  |

| R06        |                                                               |  |  |  |  |  |  |

| R07        | Vertical Sync Position                                        |  |  |  |  |  |  |

| R08        | ann an an ann an an an an an an an an an                      |  |  |  |  |  |  |

| R09        | Character Total Vertical                                      |  |  |  |  |  |  |

| R10        | Cursor Mode Cursor Stort Scon Line                            |  |  |  |  |  |  |

| R11        | Eurson End Scan Line                                          |  |  |  |  |  |  |

| R12        | Display Start Address (High)                                  |  |  |  |  |  |  |

| B13        | Display Start Address (Low)                                   |  |  |  |  |  |  |

| B14        | Cursor Position (High)                                        |  |  |  |  |  |  |

| R15        | Cursor Position (Low)                                         |  |  |  |  |  |  |

| R16        | Light Pen Verticol                                            |  |  |  |  |  |  |

| R17        | Light Pen Horizontal                                          |  |  |  |  |  |  |

| R18        | Update Location (High)                                        |  |  |  |  |  |  |

| R19        | Update Location (Low)                                         |  |  |  |  |  |  |

| R20        | Attribute Start Address (High)                                |  |  |  |  |  |  |

| R21        | Attribute Start Address (Low)                                 |  |  |  |  |  |  |

| <b>R22</b> |                                                               |  |  |  |  |  |  |

| R23        | Character Displayed-Vertical                                  |  |  |  |  |  |  |

|            |                                                               |  |  |  |  |  |  |

| R25        |                                                               |  |  |  |  |  |  |

| R26        | Foreground Color Background Color                             |  |  |  |  |  |  |

| R27        | ,                                                             |  |  |  |  |  |  |

| 82B        |                                                               |  |  |  |  |  |  |

|            |                                                               |  |  |  |  |  |  |

| R30        | Word Count (count-1)                                          |  |  |  |  |  |  |

| R31        | CPU Réad/Write Data                                           |  |  |  |  |  |  |

| R32        |                                                               |  |  |  |  |  |  |

| R33        | Block Copy Source Address (Low)                               |  |  |  |  |  |  |

|            |                                                               |  |  |  |  |  |  |

| R34 | Disploy Enable Begin       |

|-----|----------------------------|

| R35 | Display Enable End         |

| R36 | DRAM Refresh per Scon Line |

#### 8563 REGISTER MAP

37

### **8563 VIDEO CONTROLLER (Continued)**

| R/W-<br>R/W-<br>D7-<br>D6-<br>VSS-<br>D5-<br>D4-<br>D3-<br>D2-<br>D1-<br>D0-<br>D1-<br>D0-<br>NSPEN-<br>VSYNC-<br>DR/W- | 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20 | 8563<br>CRT<br>CNTRL | 40<br>39<br>37<br>36<br>35<br>32<br>30<br>30<br>29 | -DD6<br>-DD5<br>-DD4<br>-DD3<br>-DD2<br>-DD2<br>-DD1<br>-DD0<br>-DA7<br>-DA6<br>-DA5<br>-DA5<br>-DA4<br>-DA3<br>-DA3 | 13-18<br>12<br>19<br>20<br>21<br>22<br>23<br>23<br>24<br>25<br>25<br>26-33,<br>34-36,<br>34-36, | VSS<br>DISPEN<br>VSYNC<br>DR/W<br>INIT<br>RES<br>TEST<br>LPEN<br>DA0-DA7<br>DD0-DD7 | Ground.<br>Display Enable output.<br>Vertical Sync signal.<br>Local Display DRAM Read/Write.<br>Active low input for clearing internal control<br>latches.<br>Reset input that initializes all internal scan<br>counters, but not control registers.<br>Used for testing only — tied to ground.<br>Input for Light Pen. A positive going transition<br>on this input latches the vertical and horizon-<br>tal position of the character being displayed at<br>that time.<br>Local display DRAM address bus.<br>Bidirectional local display DRAM data bus. |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-                                                                                                                     | 18                                                       |                      | 31                                                 | -DA5                                                                                                                 | ~~ ~~                                                                                           | ~ . ~ .                                                                             | that time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                         |                                                          |                      |                                                    |                                                                                                                      | -                                                                                               | • ·                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DR/W-                                                                                                                   |                                                          |                      |                                                    | -DA2                                                                                                                 | 34-36,<br>38-42                                                                                 | DD0-DD7                                                                             | Bidirectional local display DRAM data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| INIT –                                                                                                                  | 22                                                       |                      | 27                                                 | –DA1                                                                                                                 | 37                                                                                              | VCC                                                                                 | 5VDC input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RES-<br>TEST-                                                                                                           |                                                          |                      |                                                    | -DAO<br>-LPEN                                                                                                        | 43-46                                                                                           | R,G,B,I                                                                             | Pixel Data Outputs. A four-bit code is formed,<br>associated with each pixel, containing col-<br>or/intensity information, allowing a total of 16                                                                                                                                                                                                                                                                                                                                                                                                         |

|    |     | colors on grey snades to be displayed. |

|----|-----|----------------------------------------|

| 47 | RAS | Row Address Strode for local DRAM.     |

| 48 | CAS | Column Address Strobe for local DRAM.  |

|                        | 906112<br>)UND IN<br>EVICE (S | TERFACE                |             |                   |                                                               |

|------------------------|-------------------------------|------------------------|-------------|-------------------|---------------------------------------------------------------|

| CAP-1A                 |                               | 28-VDD                 | 1,2,<br>3,4 | CAP1A,1B<br>2A,2B | Capacitor filter connections.                                 |

|                        |                               |                        | 5<br>6      | RES<br>Ø2         | Reset input. A low pulse initializes the SID.                 |

|                        |                               |                        | 7           | R/W               | Processor phase 2 clock input.<br>Processor read/write input. |

| $\frac{CAP}{RES} = 2B$ |                               | 25 – VCC<br>24 – POT X | 8           | CS                | Chip select input.                                            |

|                        |                               | 23 - POT Y             | 9-13        | A0-A4             | Address lines from processor.                                 |

| 02 - 6                 | 6581                          |                        | 14          | GND               | Dc ground connection.                                         |

| $R/\overline{W} - 7$   |                               | 22 – D7                | 15-22       | DO-D7             | Data Bus connections.                                         |

| <u>ČS</u> 8            | SID                           | 21  - D6               | 23          | POTY              | Input to a A/D converter used to detect the                   |

| A0- 9                  |                               | 20  - D5               |             |                   | value of a variable resistor. Commonly con-                   |

| A1-10                  |                               | 19 – D4                | 24          | POT X             | nected to game paddles.<br>Same as POT Y.                     |

POT XSame as POT Y.VCC5VDC input.EXT INExternal audio input.Audio outAudio output, AC coupled to audio amp.VDD12VDC input.

# **PIN DESCRIPTION**

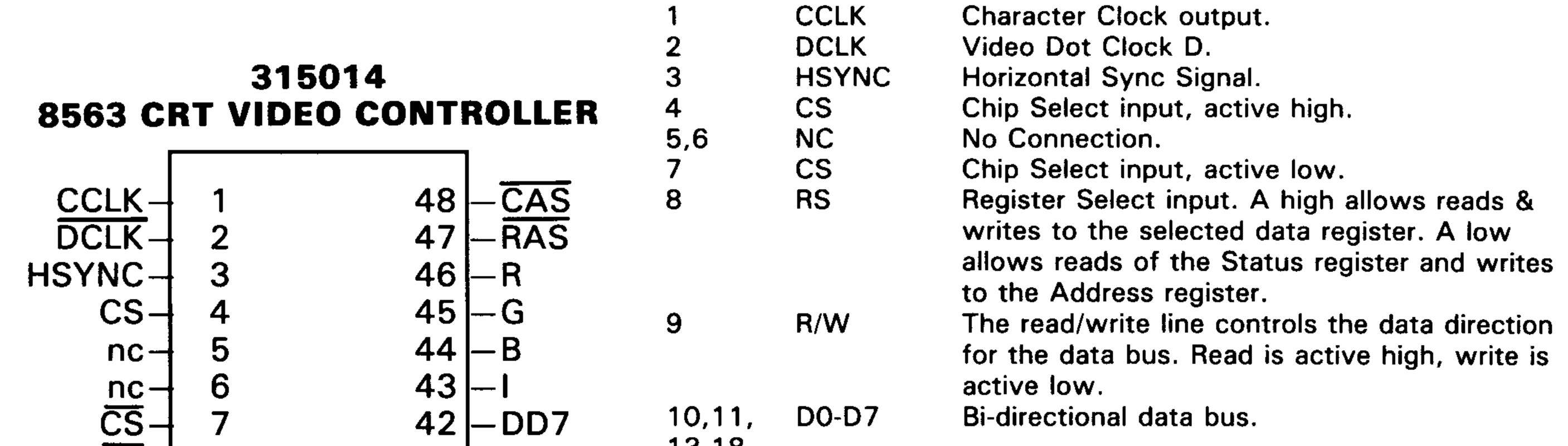

## **CPU INTERFACE**

- **D0-D7** Bidirectional Data Bus interface to the CPU.

- CS Chip Select input (active high).

- CS\* Chip Select input (active low).

- RS Register select input. A high allows reads and writes of the selected data register. A low allows reads of the Status Register and writes of the Address Register.

- R/W Read/write input to control D0-D7 data direction. A high allows the CPU to read data supplied by the CRT Controller. A low allows the CRT Controller to accept data written

by the CPU.

INTR Interrupt request output. An open-drain output that is driven low when the Update Ready status bit makes a 'zero' to 'one' transition. This output goes high-impedance when either the Update Ready status bit is a 'zero' or the CPU reads the status register.

# **VIDEO INTERFACE**

- 5 VDC + / 5%Vcc

- Vss 0 VDC

- RES Reset input to initalize all internal scan counter circuits. The control registers are not affected. RES can be used to synchronize the display frame to an externally generated signal. This signal should not be confused with the INIT input.

- LPEN Light pen input. A low-to-high transition of the LPEN input loads the internal light pen registers with the vertical and horizontal character poisitions.

- Dot clock input. Determines the pixel width, DCLK is divided internally to generate the DCLK internal character clock and DRAM signals.

- HSYNC Horizontal sync output. HSYNC polarity, position and duration are fully programmable.

- VSYNC Vertical sync output. VSYNC polarity, position and duration are fully programmable.

- CSYNC Composite SYNC output. This is the logical exculsive-nor of internal active-high HSYNC and VSYNC signals.

- R, G, B, I Red, Green, Blue and Intensity outputs. These output a four-bit code associated with each pixel. A total of 16 colors (or shades of gray) may be displayed.

- Composite Video output. This is the logical OR of the R, G, and B outputs. CV

- DR/W Video Display RAM read/write output signal.

- DD0-DD7 Video Display RAM bidirectional Data Bus.

- DA0-DA7 Video Display RAM multiplexed Address Bus outputs.

- RAS Row Address Strobe output for the multiplexed addresses.

- CAS Column address strobe output for the muliplexed addresses.

- CCLK Character clock output (for unspecified uses).

- INIT Initialization input pin (active low). Clears internal control latches, allowing the CRT Controller to begin proger operation following power-on initialization. The INIT pin should be held low for at least 16 DCLK cycles during system initialization, and held high during operation.

TEST

This pin reconfigures the part to simplify automatic testing. In normal use this pin should be connected to Vss.

40

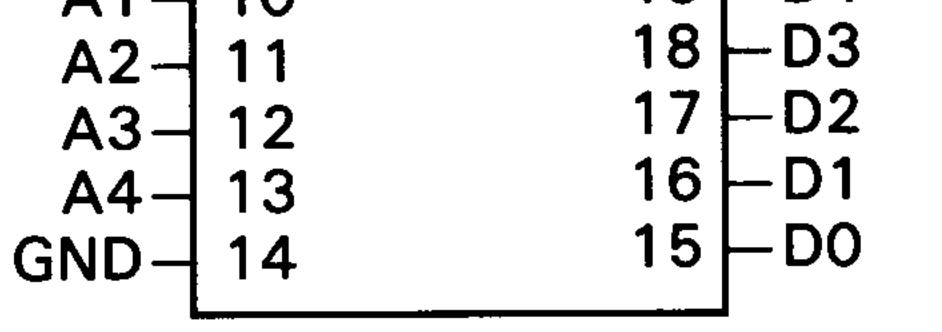

# IC 8568 **80 COLUMN CRT CONTROLLER** PN #315092-01

This Circuit implements the features of the 6545E CRT Controller with additional features to increase system integration.

39

### Features

- Single +5 volt power supply.

- Interlaced or non-interlaced display.

- NTSC or PAL operation.

- Shared RAM for Character Data, Pointers and Attributes.

- Cursor and Attributes decoded on-chip.

- R, G, B, I pixel outputs.

- Separate programmable Horizontal and Vertical Sync outputs.

- Character Clock generated on-chip.

- Interfaces to DRAMs with on-chip RAS/CAS timing.

- Programmable character fonts.

- Programmable frame height, width and rate.

- Directly interfaces to 4164 or 4416 DRAMs.

| -       |    |    | -     |

|---------|----|----|-------|

| HSYNC - | 4  | 45 | – G   |

| CS –    | 5  | 44 | — В   |

| CS*     | 6  | 43 |       |

| RS –    | 7  | 42 |       |

| R/W —   | 8  | 41 | DD6   |

| INTR    | 9  | 40 | DD5   |

| D7      | 10 | 39 | DD4   |

| D6      | 11 | 38 | - DD3 |

| Vss –   | 12 | 37 | - Vcc |

| D5 —    | 13 | 36 |       |

| D4 —    | 14 | 35 | - DD1 |

| D3 —    | 15 | 34 |       |

| D2      | 16 | 33 | DA7   |

| D1 —    | 17 | 32 | DA6   |

| D0 —    | 18 | 31 | - DA5 |

| CSYNC - | 19 | 30 | - DA4 |

| VSYNC - | 20 | 29 | - DA3 |

| DR/W    | 21 | 28 | – DA2 |

| RES -   | 22 | 27 | L DA1 |

The device is a highly integrated text display chip designed to reduce the parts count of an 80-column display system. The CRT Controller contains the high-speed pixel frequency logic, requiring only a buffer to drive low impedance loads. The CRT Controller is capable of addressing 64K of DRAM memory for Character Data (character fonts), Character Pointers and Attributes. In addition, the DRAM signals RAS, CAS, Read/Write, Data and Multiplexed Addresses are generated on-chip and require no external logic to interface to the DRAMs. The DRAM multiplexed Addresses can be configured via a programmable register bit to interface directly to either 4164 or 4416 Type DRAMs

The device contains an internal 80-column double line buffer. This buffer is loaded with Character Pointers and Attributes during the Horizontal-Blanking interval (and any blank scan lines). These Pointers and Attributes are loaded during one displayed character row for use in the next character row. This device is equivalent to a 2568 or 8568.

The -01 version of the part is intended for use in systems with a TTL level Dclk signal. The -02 version is for systems with a CMOS level Dclk.

1 2 3 Device: DVDC Part No: 8563 4 5 8568 6 7 Display Format: programmable up to up to 80x25 text, 640Hx400V bitmap (interlaced up to 80x50 text, 640Hx480V bitmap, and more) 8 9 Display Modes: 3 char modes: Std, Semigraph and pixel, 10 double width & HiRes bitmap mode Video Output: digital RGBI 16 color or 16 gray-shades Features: 8563: interlace/non-interlace, horiz & vert scroll, 11 12 lightpen input, hardware cursor, underline, blink and 13 reverse video, supports 2 character sets of 256 each 14 15 8568: above plus Update Ready Interrupt, composite video and 16 composite sync 17 Memory Interface: access 64K, programmable to interface either 4164/4464 or 18 4416 DRAM 19 Pins: 48 20 Supply: +5V 21 22 23 Make sure you get one that says R9a or R9b after the 8568. 24 These are later Revisions that seem to work better. 25 26 Pinout 27 28 Pin 8563 29 1 CCLK 30 31 2 DCLK 3 HSYN 32 33 4 /CS 5 -34 35 6 – 36 7 /CS 37 8 /RS 38 9 R/W 10 D7 39 40 11 D6 41 12 Vss D5 42 13 43 14 D4 44 15 D3 16 D2 45 17 D1 46 DO 47 18 48 19 DISPEN 20 VSYN 49 21 DR/W 50 51 22 INIT 23 /RES 52 53 24 TST 54 55 25 /LP2 56 26 DA0 57 27 DA1 58 28 DA2 59 29 DA3 60 30 DA4 61 31 DA5 62 32 DA6 33 DA7 63 64 34 DD0 35 DD1 65 36 DD2 66 Vdd 67 37 68 38 DD3 39 DD4 69 40 DD5 70 71 41 DD6 72 42 DD7 73 43 I

\_\_\_\_\_

74 44 B 75 45 G 46 R 76 77 47 /RAS 78 48 /CAS 79 80 81 82 The VDC VideoRAM Upgrade 83 84 85 From: Raymond Carlsen <rrcc@u.washington.edu> 86 Newsgroups: comp.sys.cbm 87 Subject: Re: W: 8563 RAM swap instructions 88 Date: Wed, 27 Sep 1995 20:50:02 -0700 89 90 > The subject says it all. How do you do this 16k to 64k swap? 91 92 I assume you mean the video RAM upgrade for the C-128. If you're 93 good with a de-soldering iron, it just involves removing two chips from 94 the board and installing replacements. The original chips are 4416 DRAM 95 at board locations U23 and U25 inside the metal can, between the VIC and RGB chips. The replacements are 4464. The numbers on the chips may vary 96 97 with manufacturers, but the originals are 4 bit wide 16K... two of them make 16K by 8 bits. The upgrade to two 4 bit wide 64K chips give a total 98 99 of 64K by 8 for the flat 128. The 128D was built with 64K of VRAM already 100 installed. 101 I always install sockets anytime I replace chips in a PC board. 102 Removing the old chips is the worst part of the job. Probably the easiest 103 way is to cut all of the pins on the old chip, then remove them one at a 104 time with a regular iron. As a tech, I hate to destroy anything that 105 still works. I use a desoldering iron to free each pin, then remove the 106 chip intact. If the new chips don't work for any reason, I can cross 107 check my work by reinstalling the old ones. Sockets mean never having to 108 solder again. It's important to orient the new chips in the board correctly. 109 One end of the chip will have a notch and the outline on the board will match. 110 111 Unless you have software that takes advantage of the extra video RAM 112 you will not see any difference in the performance of your computer. I 113 think Maverick uses that RAM space to speed up copying files. It's useful for improved bitmapped graphics. It is only good for the 80 column screen... 114 115 the 40 column VIC doesn't access it. To verify C-128 VRAM as either 16K or 116 64K, run this little program: 117 118 POKE DEC("D600"),28:POKE DEC("D601"),63:SYS DEC("FF62"):SCNCLR <RETURN> 119 120 If the screen shows the READY prompt and looks normal, the 128 has 64K 121 of VRAM installed. If it only has 16K (stock 128 without upgrade), the 122 screen fills up with zeros. Hit RUN/STOP-RESTORE to clear it. 123 124 At one time, some company was selling a piggyback board with the RAM 125 installed. It needed no soldering as the on-board 4116s were bypassed. All 126 that was necessary was to remove the 80 Column RGB (8563, also known as the VDC) chip from its' socket, install the piggyback board and plug the 127 128 RGB chip into the piggyback. I haven't seen that board advertised for 129 some time. 130 131 [Chips are available from Jameco Electronics @ 1-800-831-4242. Order 132 part #41582 (41464-12), or 41574 (41464-10), or 41611 (41464-80). They 133 cost less than 3 bucks each. Jameco also has other replacement chips for 134 Commodore computers.] 135 136 137 Ray Carlsen Univ. of Washington, Seattle

| 1   | Uncovered: The VDC 8568's 38th register                                                                                        |

|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 2   | Ok you,re probably already thinking, "but the VDC has only 37 registers, hasn't it?"                                           |

| 3   | This is quite correct for the old 8563 types inside the C128 and C128D.                                                        |

| 4   | Inside the C128DCR, however, a later version with different new characteristics had been installed.                            |

| 5   | One of them is an additional register!                                                                                         |

| 6   | one of them is an additional register:                                                                                         |

| 7   | by Nicolas Welte                                                                                                               |

| 8   | The existance of register 37 (you start counting at 0) had already been reported                                               |

|     | about by 64'er magazine,                                                                                                       |

| 9   | but there hasn't even been a hint of an explanation of the register's function.                                                |

| 10  | This should finally be made up for with this article.                                                                          |

| 11  | Only bits 7 and 6 are available, all other bits are 'reserved' and will always read back as 1.                                 |

| 12  | Following a hardware reset, though, bits 7 and 6 are also 1,                                                                   |

| 13  | so that reading the register will return 255 just as with all other unused registers.                                          |

| 14  | Only when writing into the register, the difference will become apparent,                                                      |

| 15  | and in a really big way to boot: the screen loses synchronization and the picture                                              |

|     | runs through.                                                                                                                  |

| 16  | This is not a useful effect, of course.                                                                                        |

| 17  | Some measuring at video output returned the following function: bit 7 controls the                                             |

|     | horizontal sync signal's polarity.                                                                                             |

| 18  | That signal is found at the RGBI connector. In the same way, the vertical sync signal at pin 9 is controlled by bit 6.         |

| 19  | In this case, polarity refers to whether the synchronisation pulse is directed from                                            |

|     | TTL 0 to 1 (positive) or from 1 to 0 (negative).                                                                               |

| 20  | By default, the C128 works with positive pulses for both signals, and all monitors are designed for that.                      |

| 21  | This leads to following register map, which you should glue into the manual:                                                   |

| 22  | [table is printed in the issue]                                                                                                |

| 23  | Is there any advantage we can get from this register? Yes, indeed there is!                                                    |

| 24  | But in order to gain it, you need an EGA monitor.                                                                              |

| 25  | EGA monitors were the first high resolution monitors for PCs that really deserved                                              |

|     | the name.                                                                                                                      |

| 26  | These monitors work with two different fixed frequency modes, one of which is                                                  |

|     | comaptible with older CGA cards,                                                                                               |

| 27  | and therefore with the C128's RGBI output.                                                                                     |

| 28  | The other mode works at a line frequency of about 21kHz and a resolution of 640x350                                            |

| 29  | at a vertical refresh rate of 60Hz, though.<br>EGA also offers 64 colors instead of just 16 colors, but of course this feature |

| 29  | can't be used by a C128.                                                                                                       |

| 30  | Some C128 owners may be using such a monitor, as they offer a better display quality                                           |

| 00  | than older CGA models.                                                                                                         |

| 31  | These days, they can be bought for a song as well.                                                                             |

| 32  | How does the EGA monitor know in which of its two modes it should work? One option                                             |

|     | would be an automatic detection of the line frequency,                                                                         |

| 33  | but the time hadn't come for that technology yet.                                                                              |

| 34  | Thus, the monitor needed a signal from the outside indicating which mode should be                                             |

| 0 - | chosen.                                                                                                                        |

| 35  | This is realized by the sync signals' polarity!                                                                                |

| 36  | Four different modes could therefore be chosen, but my monitor in particular knows                                             |

| 37  | only two.<br>There are also modern multi frequency monitors which ignore this signaling and                                    |

| 57  | switch automatically.                                                                                                          |

| 38  | There are two example programs on the cover disk, which will only run on a C128DCR.                                            |

| 39  | Those of you who are sure you have a monitor which switches automatically, may                                                 |

|     | remove line 5 from the program, which will allow the programs to run on old C128s                                              |

|     | and C128Ds.                                                                                                                    |

| 40  | In all cases, you should be absolutely sure that a monitor is connected which can                                              |

|     | handle 21kHz, otherwise, there can be significant damage!                                                                      |

| 41  | Two different versions are given, a 50Hz version and a 60Hz version, sensibly named                                            |

| 42  | EGA50HZ and EGA60HZ.<br>The 60Hz version displays a text screen with 77 columns and 43 lines roughly                           |

|     | resembling PC's EGA standard.                                                                                                  |

| 43  | At least for me, the 50Hz version works better, perhaps due to the fact that I have                                            |

|     | a 50Hz mains current as well.                                                                                                  |

| 44  | This allows for 77 columns and 52 lines, without any interlace flickering!                                                     |

|     | Unfortunately, 77 columns are the absolute maximum with attributes turned off.                                                 |

| 45  | [Deed more shout this tenis is the surrent OOCAL issue]                                                                        |

| 46  | [Read more about this topic in the current GO64!-issue]                                                                        |