| APPLIC     | CATION  | REVISION |                                      |         |          |  |  |  |

|------------|---------|----------|--------------------------------------|---------|----------|--|--|--|

| NEXT ASSY. | USED ON | LTR      | DESCRIPTION                          | DATE    | APPROVED |  |  |  |

|            | C64     | A        | SPECIFICATION RELEASE PER ECO 850152 | 7-19-90 | RMB      |  |  |  |

|            |         | В        | REVISED PER ECO 900376               | 5-8-91  | RMB      |  |  |  |

|            |         |          |                                      |         |          |  |  |  |

# 1.0 DESCRIPTION

This IC Memory Controller incorporates the functions of Commodore part number 251715 (used on the C64E models) and has 4K of static RAM (SRAM).

# 1.2 CONFIGURATION

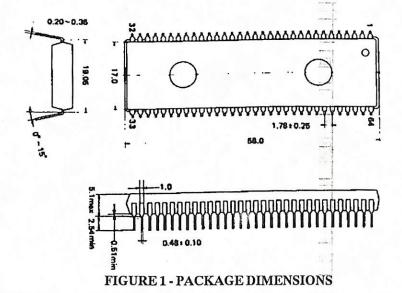

This device is configured as a 64 pin plastic DIP.

# 2.0 SOURCES

Refer to Approved Vendor List for sources.

| COMMODORE P. N.                                                                                                                                                                                                                                          | STATUS   |                           |        |           |                                                                |                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|--------|-----------|----------------------------------------------------------------|------------------------|--|

| - 252535-01                                                                                                                                                                                                                                              | ACTIVE   |                           |        |           |                                                                |                        |  |

|                                                                                                                                                                                                                                                          |          |                           | 70     |           |                                                                |                        |  |

|                                                                                                                                                                                                                                                          |          |                           | TS     | ,         |                                                                |                        |  |

| UNLESS OTHERWISE SPECIFIED DIMENSIONS ARE IN INCHES. TOLERANCES: ANGLES +/- 1 DEGREE 2 PLACE DECIMALS +/- 0.02 3 PLACE DECIMALS +/- 0.010                                                                                                                |          | DRAWN<br>Mike Rivers      | DATE   | C         | omr                                                            | nodore                 |  |

|                                                                                                                                                                                                                                                          |          | SYSTEM ENG.               | DATE P |           | 1200 WILSON DRIVE<br>WEST CHESTER, PA. 19380<br>(215) 431-9100 |                        |  |

|                                                                                                                                                                                                                                                          |          | TEST ENG                  | DATE   |           |                                                                |                        |  |

| PYRIGHT 1990<br>MMODORE ELECTRON                                                                                                                                                                                                                         | IICS LTD | COMP. ENG<br>Drew Shannon | DATE   | TITLE:    |                                                                |                        |  |

| INFORMATION CONTAINED HEREIN IS THE UN- PUBLISHED AND CONFIDENTIAL PROPERTY OF COMMODORE ELECTRONICS LIMITED. USE, REPRODUCTION OR DISCLOSURE OF THIS INFORMA- TION WITHOUT THE PRIOR WRITTEN PERMISSION OF COMMODORE IS STRICTLY PROHIBITED. ALL RIGHTS |          | CIRCUIT ENG.              | DATE   | IC,       | IC, MEMORY CONTROLLER<br>W/SRAM                                |                        |  |

|                                                                                                                                                                                                                                                          |          |                           | )r     | SIZE<br>A | DRAWING                                                        |                        |  |

| ESERVED.                                                                                                                                                                                                                                                 |          |                           |        | SCAL      | E                                                              | 252535<br>SHEET 1 OF 5 |  |

### 3.0 JUMPER CONFIGURATION (C64 NEW PCB)

- J10: Address A14 line for 256K ROM from memory controller. Normally open, shorted if 256K of ROM is used.

- J11: Pull-up to 5V for 128K ROM, PIN 27. Normally shorted, open if 256K ROM is used.

- J12: Address A13 line for 128K ROM from CPU. Normally shorted, opened if 256K ROM is used.

- J13: Address A13 line for 256K ROM from Memory Controller. Normally open, shorted if 256K of ROM is used.

- J14: Chip Select (CS) line for 32 K ROM from Memory Controller. Normally short, open if 256K ROM is used.

- J15: ROM Select (128K ROM and 32K ROM, or 256K ROM). Normally shorted, open if 256K ROM is used.

- J16: ROM select (128K ROM and 32K ROM or 256K ROM). normally open, shorted if 256K ROM is used.

- J17: Select input or output mode on color RAM select line and select ROM chip select (CS) line for 128K ROM or 64K ROM on KER/ROM output.

- J18: To swap address space if A14 and A13 are high. Normally open, address \$8000 is accessed if shorted, and A13 and A14 are high.

### 32K character and 128 Kernal/Basic ROM

- J10: OPEN

- J11: SHORT

- J12: SHORT

- J13: OPEN

- J14: SHORT

- J15: SHORT

- J16: OPEN J17: SHORT

- J18: OPEN (DON'T CARE)

### 256K CHARACTER/KERNAL/BASIC ROM

- J10: SHORT

- J11: OPEN

- J12: OPEN

- J13: SHORT

- J14: OPEN

- J15: OPEN

- J16: SHORT

- J17: SHORT

- J18: SHORT

# Commodore

TITLE

CR

# IC, MEMORY CONTROLLER W/SRAM

| ZE | DRAWING NUMBER | REV. | SCALE | liv | SHEET 2 OF 5 |

|----|----------------|------|-------|-----|--------------|

|    | 252535         | В    |       |     |              |

# TABLE 1 - JUMPER CONFIGURATION

|                         |                                               | 128K<br>&<br>32K ROM                         | 256K ROM                          | 128K ROM &<br>32K ROM WITH<br>4K SRAM | INHIBIT    |

|-------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------|---------------------------------------|------------|

| JUMPER<br>CONFIGURATION | J15                                           | SHORT                                        | OPEN                              | SHORT                                 | DON'T CARE |

|                         | J16                                           | OPEN                                         | SHORT                             | OPEN                                  | SHORT      |

|                         | J17                                           | SHORT                                        | SHORT                             | OPEN                                  | OPEN       |

|                         | J18                                           | DON'T CARE<br>(INPUT)                        | SHORT<br>(INPUT)                  | SHORT (OUTPUT)                        |            |

| INPUT/OUTPUT SIGNAL     | CARM/AI13<br>BAS/AI14<br>KER/ROM<br>CLRM/DMDE | CARM BAS  *2 KER (KERNAL+BASIC) DMDE (INPUT) | A13<br>A14<br>ROM<br>DMDE (INPUT) | CARM  BAS  KER  CLRM (OUTPUT)         |            |

NOTE 1. CARM is the chip select signal (CS) for CHAR ROM

BAS is the chip select signal (CS) for BASIC ROM

KER is the chip select signal (CS) for KERNAL ROM

ROM is the chip select signal (CS) for combined 256K ROM

2. \*2 KER is the KERNAL and BASIC OR-ed signal

|     | Commodore      |      | IC, MEM | ORY CONTROLLER W/SRAM |

|-----|----------------|------|---------|-----------------------|

| IZE | DRAWING NUMBER | REV. | SCALE   | SHEET 3 OF 5          |

|     | 252535         | В    |         |                       |

# 3.2 PIN DESCRIPTIONS

SIZE

| 1  | A13        | 33 | VSS    |

|----|------------|----|--------|

| 2  | A14        | 34 | A10    |

| 3  | A15        | 35 | -CAS   |

| 4  | R/-W       | 36 | -RAS   |

| 5  | -LORAM     | 37 | φ0     |

| 6  | -HIRAM     | 38 | AEC    |

| 7  | -CHAREN    | 39 | BA     |

| 8  | NHI        | 40 | -VIC   |

| 9  | RESTOR     | 41 | VA6    |

| 10 | -VA14      | 42 | VA7    |

| 11 | -VA15      | 43 | -SID   |

| 12 | -CIA12     | 44 | -ROML  |

| 13 | -CHAROM    | 45 | -I/O2  |

| 14 | -BASIC     | 46 | -EXROM |

| 15 | -KERNAL    | 47 | -GAME  |

| 16 | VSS        | 48 | VSS    |

| 17 | -CLRM/DMD8 | 49 | -I/O1  |

| 18 | I/O 1      | 50 | -ROMH  |

| 19 | I/O 2      | 51 | A0     |

| 20 | I/O 3      | 52 | A1     |

| 21 | I/O 4      | 53 | A2     |

| 22 | -CASRAM    | 54 | A3     |

| 23 | RAM R/-W   | 55 | A4     |

| 24 | MA6        | 56 | A5     |

| 25 | MA3        | 57 | A6     |

| 26 | MA0        | 58 | A7     |

| 27 | MA2        | 59 | A8     |

| 28 | MA4        | 60 | A9     |

| 29 | MA1        | 61 | A10    |

| 30 | MA5        | 62 | A11    |

| 31 | MA7        | 63 | A12    |

| 32 | N/C        | 64 | VDD    |

| Commodore      |      | IC, MEMORY CONTROLLER W/SRAM |              |  |

|----------------|------|------------------------------|--------------|--|

| DRAWING NUMBER | REV. | SCALE                        | SHEET 4 OF 5 |  |

| 252535         | В    |                              |              |  |

### 4.0 ENVIRONMENTAL REQUIREMENTS

Units furnished to the requirements of this specification shall meet the following environmental resistance requirements (vendors shall furnish supporting documentation upon request):

Operating Temperature

0 to 70 deg. C

Operating Humidity

5 to 95% RH non-condensing

2011

Operating Altitude

0 to 3000 meters - 20 to + 85 deg. C

Storage Temperature Storage Humidity

5 to 95% RH non-condensing

Storage Altitude

0 to 15,000 meters

### 4.1 PROCESS QUALIFICATION TESTS

Integrated circuits supplied to the requirements of this specification shall meet the requirements of Engineering Policy No. 1.02.008. Supporting documentation shall be supplied by vendor upon request.

### 4.2 ENVIRONMENTAL TEST CONDITIONS

Devices shall comply with the following environmental resistance tests per Commodore Engineering Policy 1.02.007.

- 1. Temperature/humidity (85 deg. C and 95% RH non-condensing) for 168 hours.

- 2. Operating life (1000 hours at 70 deg. C ambient temperature)

- 3. Solderability per MIL-STD-883, Method 2003

- 4. Pressure cooker (15 psig, 120 deg. C, and 100% RH for 24 hours)

- 5. Solvent resistance per MIL-STD-883, Method 2015, using water and trichloroethane

- 6. Solder temperature resistance (250 deg. C for five seconds)

Note: Devices shall meet this specification's operating performance requirements after the above tests are completed.

### 4.3 MINIMUM ACCEPTANCE LEVEL

The minimum acceptance level of any lot shall be an AQL of 0.65 as defined by MIL-STD 105 single sampling techniques.

### 4.4 MARKINGS

Devices shall be marked with manufacturer's part number and EIA date code  $\frac{1}{110}$

#### 4.5 AGE OF DEVICES

Unit shall be rejected if EIA Date Code indicates an age of three (3) or more years.

|   | Commodore      |      | IC, MEMORY CONTROLLER W/SRAM |              |  |

|---|----------------|------|------------------------------|--------------|--|

| E | DRAWING NUMBER | REV. | SCALE                        | SHEET 5 OF 5 |  |

|   | 252535         | В    |                              |              |  |

# APPROVED VENDOR LIST

This sheet must be removed from this document before the document is shown or transmitted to a vendor.

Commodore Part Number

Vendor

Vendor Part Number

252535-01

SANYO

3AB9600-S252

ıt is .

|     | Commodore      | IC, MEMORY CONTROLLER W/SRAM |       |              |

|-----|----------------|------------------------------|-------|--------------|

| IZE | DRAWING NUMBER | REV.                         | SCALE | SHEET i OF i |

|     | 252535         | В                            |       |              |